ベン アブダラ アブデラゼク BEN ABDALLAH Abderazek

教授、理事(教育・学務担当)、コンピュータ理工学部学 部長、コンピュータ理工学部学 コンピュータ理工学科長

- 所属

- コンピュータ理工学科/コンピュータ工学部門

- 職位

- 教授、理事(教育・学務担当)、コンピュータ理工学部学 部長、コンピュータ理工学部学 コンピュータ理工学科長

- benab@u-aizu.ac.jp

教育

- 担当科目 - 大学

- - コンピュータアーキテクチャ, 2018 -

- コンピュータシステム入門, 2018 -

- 並列計算機システム, 2018 -

- SCCP-001 – 学生協同授業プロジェクト(システムオンチップ設計), 2009-2010

- コンピュータシステム工学, 2008-2018

- 組み込みシステム, 2008-2016

- 論理回路設計演習, 2008-2018

- コンピュータアーキテクチャ演習, 2008-2018

- 担当科目 - 大学院

- - ニューロモーフィックコンピューティング, 2023 – present

- 組み込みリアルタイム システム, 2008 – 2022

- マルチコアコンピューティング, 2010-2015

- 高度なコンピュータ組織, 2008 – 2023

- Network-on-Chip, Hong Kong University of Science and Technology (KUST), Hong Kong, China, 2010, 2011, 2012, 2013 (Invited intensive lectures)

研究

- 研究分野

-

計算機システム

高性能計算

知能ロボティクス

- 略歴

- 令和4年4月~現在 理事 会津大学

令和4年4月~現在 コンピュータ理工学部長,会津大学

2014.4-現在 教育研究評議会委員、会津大学

2014.4-2022.03 コンピュータ工学部門長, 会津大学

2014.4-現在 教授、会津大学

2012.4-2014.3 上級准教授、会津大学

2011.4-2012.3 准教授、会津大学

2007.10-2011.3 助教授、会津大学, 会津若松

2007.4-2007.9 助教授、国立大学法人電気通信大学,東京

2002.4-2007.3 研究員、国立大学法人電気通信大学,東京

招待講師

令和4年-現在 非常勤講師, 京都工芸繊維大学 大学院工芸科学研究科

2011-2015 客員教授、软件工程学院, 华中科技大学,武漢

2010-2013 客員教授、计算机科学与工程系, 香港科技大学,香港

教育資格

1999.4-2002.3 博士 (コンピュータ工学), 国立大学法人電気通信大学,東京

1994.9-1997.6 博士前 (コンピュータ工学), 华中科技大学, 武漢

1988.9-1994.6 学部 (電気工学),スファックス大学と华中科技大学, 武漢

- 現在の研究課題

- 適応型リアルタイムニューロモーフィックプロテーゼおよび擬人化システム/ロボット工学の手法の研究開発

- 研究内容キーワード

- 3D-IC; 耐障害性。 ネットワークオンチップ。 コンピュータシステム; マルチコア SoC; ニューロモーフィック コンピューティング。 擬人化ロボット工学

- 所属学会

- IEEEシニアメンバー; ACMシニアメンバー; IEEE Circuits and Systems, IEEE Solid-State Circuits Society(メンバー); IEEE Computer Societyコンピュータアーキテクチャに関する技術委員会(メンバー); 欧州イノベーション同盟 (メンバー); 電子情報通信学会 (メンバー 2007-2019)

パーソナルデータ

- 趣味

- 歴史的な場所の閲覧と訪問.

- 子供時代の夢

- 学校の先生になる!

- 座右の銘

- シンプルがベストです!

- 愛読書

- "You Can Heal Your Life"

- 学生へのメッセージ

- 集中と組織は、あなたの研究の成功の鍵です。

主な研究

- AI を活用した分散型エネルギーハーベスティング

-

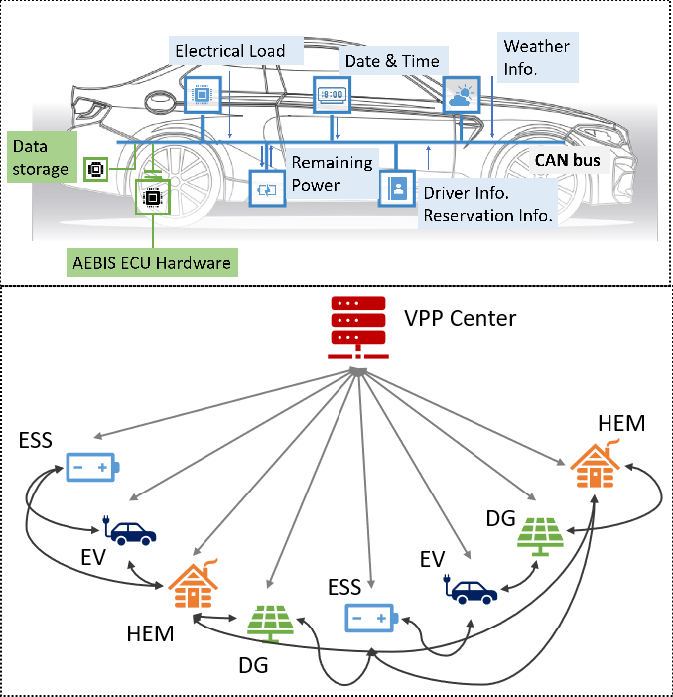

本プロジェクトでは、株式会社会津コンピュータ科学研究所、株式会社播州ジャパンと共同で、EVとソーラーカーポートに基づくスマートグリッドプラットフォームにおける電力管理のためのAI対応、ブロックチェーンベースの電気自動車統合システムの開発を行っています。EVフリートが電気エネルギーの消費者としても供給者としても採用されるEV充電予測のために、低消費電力のAIチップと各種ソフトウェアツールを開発しました。

- ネットワークオンチップ向けの高度な相互接続技術 (2D, 3D, Si-Photonics、ハイブリッド)

-

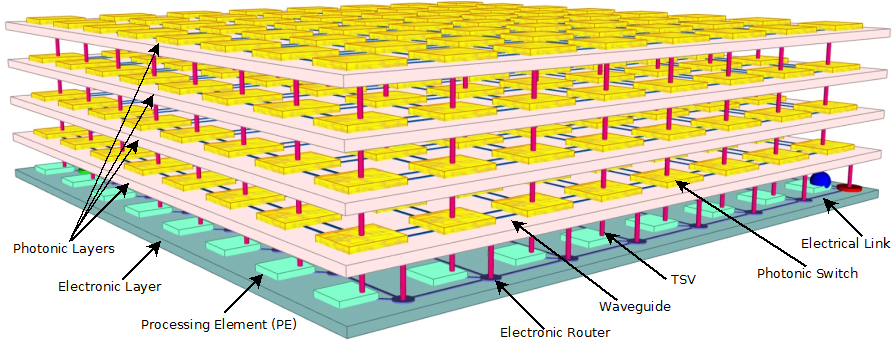

複雑な SoC には、プロセッサ コア、DSP、メモリ、アクセラレータ、および I/O で構成される多数のコンポーネントが含まれており、すべてがわずか数平方ミリメートルの単一のダイ領域に統合されています。 このような複雑なシステムは、現在のバスベースのソリューションよりも洗練されたネットワークに近い複雑なオンチップ相互接続を介して相互接続されます。 このネットワークは、面積と消費電力を低く抑えながら、高スループットと低遅延を提供する必要があります。 私たちの研究努力は、超並列メニーコア システムでこのような新しいパラダイムを可能にするために、いくつかの設計上の課題を解決することです。 特に、フォールト トレランス、3D-TSV 統合、フォトニック通信、低電力マッピング技術、および低遅延適応ルーティングを調査しています。

- 3D スパイキング ニューロモーフィック プロセッサ

-

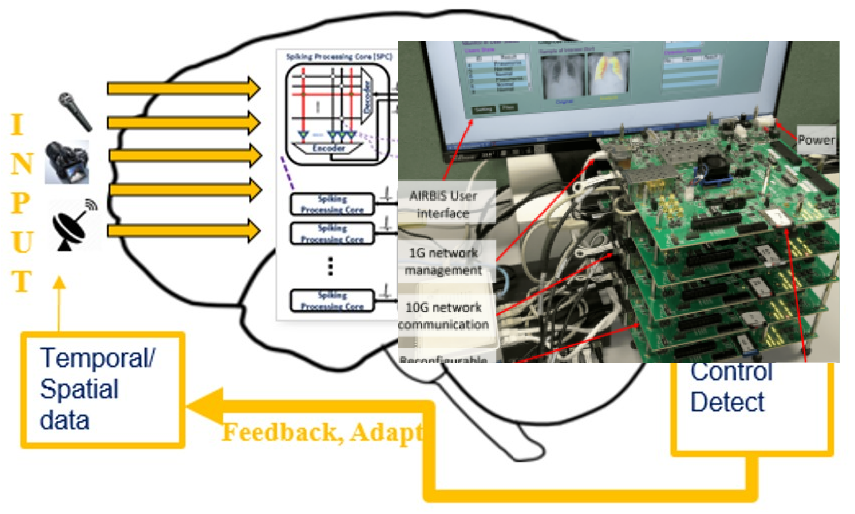

ニューロモーフィック コンピューティングでは、Spiking Neuron Network モデルを使用して、従来の人工ニューラル ネットワークと比較して、より電力/エネルギー効率の高い方法で機械学習の問題を解決します。

このプロジェクトの目的は、先に開発したフォールト トレラントな 3 次元オンチップ インターコネクト技術を活用した、適応型低電力スパイキング ニューラル ネットワーク システム イン ハードウェア (NASH) の研究開発です。 NASH システムの特徴は次のとおりです。(1) さまざまな SNN パラメーター (スパイクの重み、ルーティング、隠れ層、トポロジなど) の再構成を可能にする効率的な適応構成方法 (2) さまざまなディープ NN トポロジーの混合 ( 3) 効率的なフォールト トレラント マルチキャスト スパイク ルーティング アルゴリズム。(4) 効率的なオンチップ学習メカニズム。

NASH システムの性能を実証するために、FPGA 実装を開発し、VLSI 実装も確立する必要があります。

- AIzuHand: 適応型リアルタイム非侵襲的ニューロモルフィック神経人工手

-

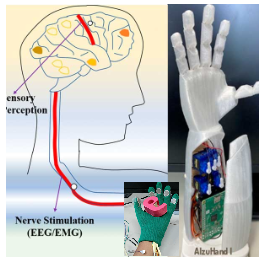

切断や神経障害のある人々の握力と動きを回復することは、自立を取り戻すために不可欠です。 治療法として広く普及しつつある義肢は、切断や神経障害のある人々の握力を大幅に回復させ、生活の質を向上させることができます。 ただし、さまざまな感覚入力を組み合わせて複雑なタスクを正確に実行する生体エージェントとは異なり、ほとんどのプロテーゼは単感覚入力を使用し、自由度が限られており、長い患者訓練が必要です。

私たちは、切断や神経障害を持つ人々の把握力と感覚を回復するための適応義肢を研究しています。 特に、残存した腕や脚と環境を直接接続する非侵襲的技術を開発します。

主な著書・論文

論文リストは研究室のウェブサイトをご覧ください Link.