Neuromorphic AI Circuits and Systems

Overview

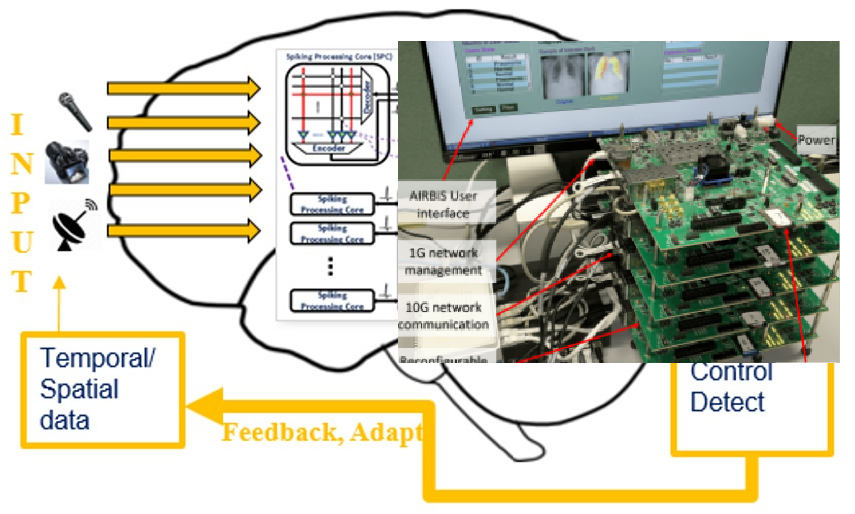

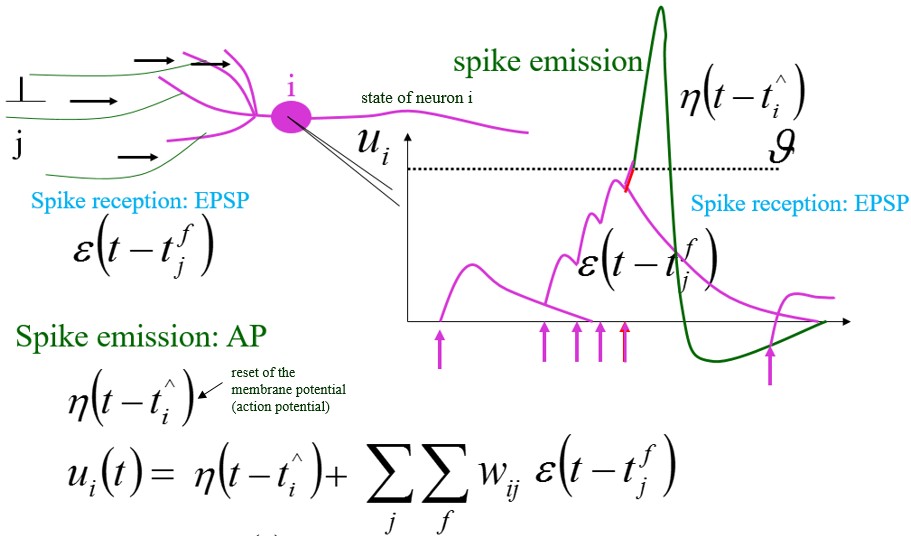

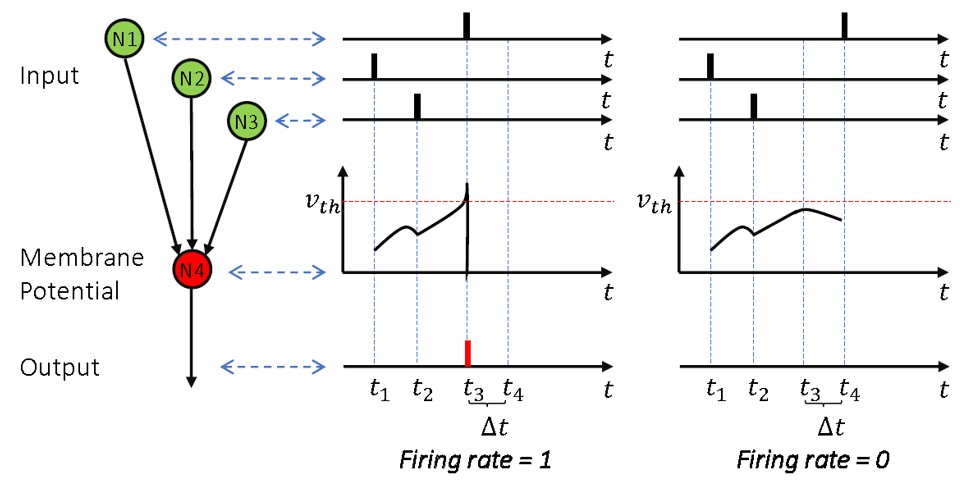

We are exploring the development of an adaptive ultra-low power neuromorphic chip (NASH) and systems, enhanced by our previously developed fault-tolerant three-dimensional on-chip interconnect technology. The NASH system boasts several features, including an efficient adaptive configuration method that enables the reconfiguration of various SNN parameters such as spike weights, routing, hidden layers, and topology. Additionally, the system incorporates a blend of different deep neural network topologies, an efficient fault-tolerant multicast spike routing algorithm, and an effective on-chip learning mechanism. To demonstrate the performance of the NASH system, we will develop an FPGA implementation and establish a VLSI implementation. The ultimate goal of NASH is to bring brain-inspired processing technology to small-scale embedded sensors and sensor-based devices, such as BCI (EEG/EMG), audio, presence detection, and activity recognition.

...read more